High-breakdown slanted tri-gate gallium nitride power transistors

© 2019 EPFL

Our demonstration of High-breakdown slanted tri-gate gallium nitride power transistors was featured on SemiconductorToday magazine - Aug. 2017

Jun Ma and Elison Matioli of the École Polytechnique Fédérale de Lausanne in Switzerland have used slanted tri-gate structures to enhance the breakdown voltage of gallium nitride (GaN) metal-oxide-semiconductor high-electron-mobility transistors (MOSHEMTs) by 500V [IEEE Electron Device Letters, published online 25 July 2017]. They claim a record 1.2GW/cm2 high-power figure of merit.

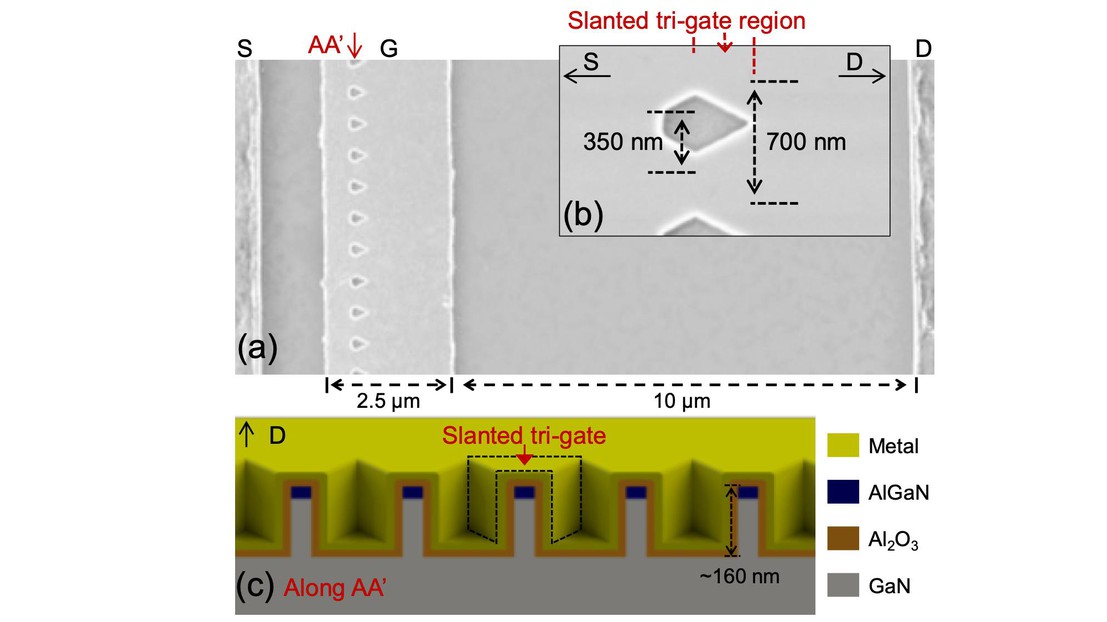

The fabricated transistors (Figure 1) consisted of etched nanowires with slanted width within the gate region. The etch depth was 160nm into the aluminium gallium nitride (AlGaN) barrier on gallium nitride channel on silicon structure. The slant gave a 350nm width on the source side and 700nm on the drain side.

The gate stack consisted of 20nm atomic layer deposition (ALD) aluminium oxide (Al2O3) and metal wrapped around the channel. The source and drain planar sides of the gate were 0.5\micron and 1.5\micron, respectively. The total gate length was 2.5\micron. The source-gate and gate-drain distances were 1.5\micron and 10\micron, respectively.

Since the researchers were interested in the raw effect of slant gates, they did not use conventional field plates or passivation. In fact, the team sees the tri-gate structure as converting the planar part of the gate towards the drain side into an effective field plate. The slant structure allows the pinch-off potential to vary in such a way that the electric field is kept below critical. The varying potential is mainly achieved by strain relaxation in the AlGaN/GaN nanowires along with the increased electrostatic control offered by the sidewall gates of the tri-gate structure.

Without field plates, or the slant tri-gate structure, the electric field tends to peak at the gate edge on the drain side. However, while field plates require complex processing, tri-gates can be achieved with just one extra etch step.

Even introducing an unslanted tri-gate into the planar transistor improved the breakdown voltage from 877V to 1100V with a 1microA/mm leakage criterion. Slanting the tri-gates increased the breakdown further to 1350V, close to the buffer limit, even with a gate-drain distance as low as 10\micron.

European Research Council under the European Union’s H2020 program/ERC grant Agreement 679425 and the Swiss National Science Foundation under Assistant Professor (AP) Energy Grant PYAPP2_166901.

J. Ma; E. Matioli : Slanted Tri-gates for High-Voltage GaN Power Devices; IEEE Electron Device Letters, 38, 9, 1305-1308 2017. DOI : 10.1109/LED.2017.2731799.