Jumpstarting computers with 3D chips

© 2012 EPFL

EPFL scientists have developed a new generation of 3D computer chips, stacked vertically rather than placed side by side. Thanks to this technology, computers will be faster, more efficient and capable of carrying out more tasks simultaneously.

EPFL scientist are among the leaders in the race to develop an industry-ready prototype of a 3D chip as well as a high-performance and reliable manufacturing method. The chip is composed of three or more processors that are stacked vertically and connected together—resulting in increased speed and multitasking, more memory and calculating power, better functionality and wireless connectivity.

Developed at the Microelectronics Systems Laboratory (LSM), Director Yusuf Leblebici is unveiling these results to experts today in Paris, in a keynote presentation at the 2012 Interconnection Network Architectures Workshop.

“It’s the logical next step in electronics development, because it allows a large increase in terms of efficiency,” says Leblebici.

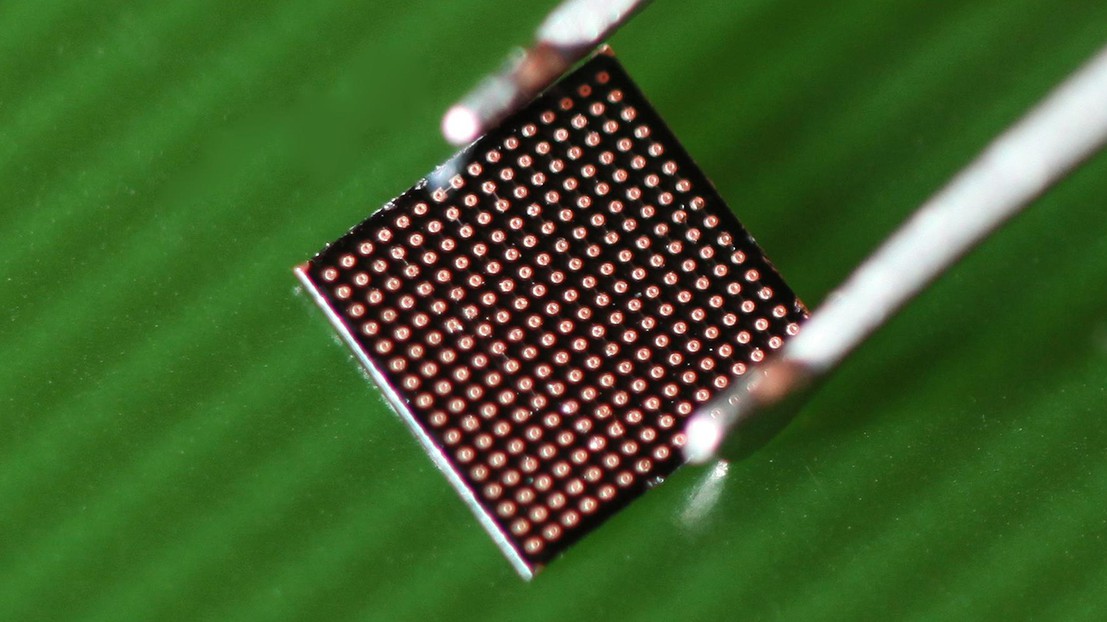

Up to this point, chips could only be assembled horizontally via connections along their edges. Here, they are connected vertically by several hundred very thin copper pillars. These wires pass through tiny openings, called Through-Silicon-Vias (TSV), made in the core of the silicon layer of each chip.

3D processors

“This superposition reduces the distance between circuits, and thus considerably improves the speed of data exchange,” explains LSM researcher Yuksel Temiz, who is doing his PhD thesis on the subject.

To reach this result, the team had to overcome a number of difficulties, such as the fragility of the copper connections and supports which, because they are miniaturized to such an extreme degree (about 50 micrometers in thickness), are as thin as a human hair. “In three years of work, we made and tested thousands of TSV connections, and had more than 900 functioning simultaneously,” says Leblebici. “Now we have a production process that is really efficient.” He adds that the laboratory has also manufactured 3D multi-core processors, connected by a TSV network.

This technology will initially be made available to a number of academic research teams for further development, before being commercialized.